# Computer Organization and Architecture, Pt. <u>1</u>

Charles Abzug, Ph.D.

Department of Computer Science James Madison University Harrisonburg, VA 22807

Voice Phone: 540-568-8746, E-mail: CharlesAbzug@ACM.org Home Page: http://www.cs.jmu.edu/users/abzugcx

© 2001 Charles Abzug

## Carpinelli Table 1.1: BASIC BOOLEAN FUNCTIONS I

## Carpinelli Table 1.2: BASIC BOOLEAN FUNCTIONS II

#### Notation for Boolean Logical Operations

A' =

$$\overline{A}$$

=  $\neg A$  =  $!A$  = NOT A

XVY = X+Y = XOR Y

XAY = X•Y = XY = XAND Y

XNAND Y

X $\oplus$ Y = XXOR Y

XXNOR Y

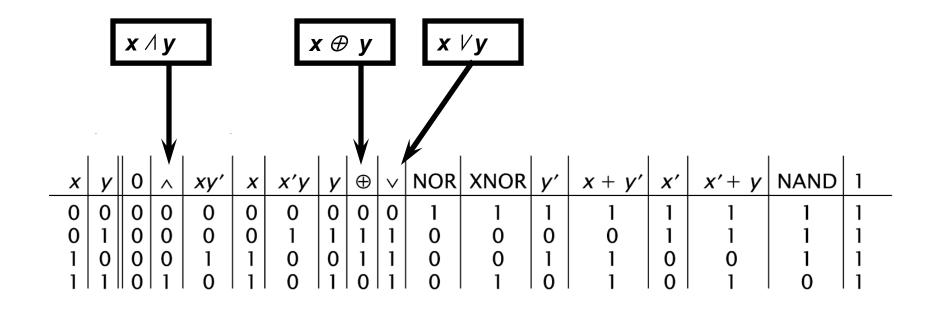

## Carpinelli Table 1.3: ALL POSSIBLE BOOLEAN FUNCTIONS of TWO INPUT VARIABLES

## Carpinelli Table 1.4: TRUTH TABLE for a COMPOSITE BOOLEAN FUNCTION

$F(x,y) = x \bullet y' + y \bullet z$

## Carpinelli Table 1.5: TRUTH TABLE for another COMPOSITE BOOLEAN FUNCTION

$F(x,y) = (x + y') \cdot (y + z)$

## Carpinelli Table 1.6: TRUTH TABLES DEMONSTRATING ALGEBRAIC EQUIVALENCES RESULTING from DeMORGAN'S THEOREMS

$F(x,y) = (x \bullet y' + y \bullet z)' = (x' + y) \bullet (y' + z) = x' \bullet y' + x' \bullet z' + y \bullet z'$

Carpinelli Figure 1.1: BASIC KARNAUGH MAPS (3-variable and 4-variable)

#### Carpinelli Figure 1.2: GENERATION of GRAY CODE

## Carpinelli Figure 1.3: SAMPLE <u>3</u>-VARIABLE KARNAUGH MAP SHOWING ALGEBRAIC SIMPLIFICATION

## Carpinelli Figure 1.4: SAMPLE <u>4</u>-VARIABLE KARNAUGH MAP SHOWING ALGEBRAIC SIMPLIFICATION

## Carpinelli Figure 1.5 : ANOTHER <u>4</u>-VARIABLE KARNAUGH MAP SHOWING ALGEBRAIC SIMPLIFICATION

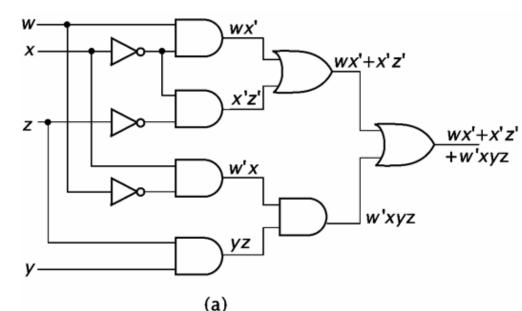

## Carpinelli Figure 1.7: LOGIC CIRCUITS IMPLEMENTING a BOOLEAN FUNCTION

## Carpinelli Figure 1.7: LOGIC CIRCUITS IMPLEMENTING a BOOLEAN FUNCTION

NOTE: This is a three-stage circuit — first stage AND gates, second stage one OR and one AND gate, third stage an OR gate. This is <u>not</u> how we implement a Boolean function normally.

Original figure or table © 2001 by Addison Wesley Longman, Inc

This is a normal logic-circuit implementation of a Boolean function.

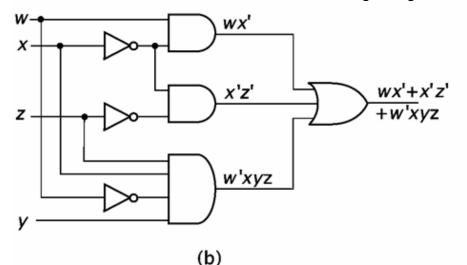

#### Carpinelli Figure 1.8: SIMPLE BUFFER GATE and TRI-STATE GATES

## Carpinelli Table 1.7, as it appears in the text: TRUTH TABLES for BUFFER GATES

Simple Buffer Gate

Tri-State Buffer (Active-High Enable)

Tri-State Buffer (Active-Low Enable)

## Carpinelli Table 1.7, TRUTH TABLES FOR BUFFER GATES CORRECTED to COUNTING ORDER:

Original figure or table © 2001 by Addison Wesley Longman, Inc

Truth Tables in Counting Order:

| Ε | In | Out |

|---|----|-----|

| 0 | X  | Ζ   |

| 1 | 0  | 0   |

| 1 | 1  | 1   |

| Ε | In | Out |

|---|----|-----|

| 0 | 0  | 0   |

| 0 | 1  | 1   |

| 1 | X  | Ζ   |

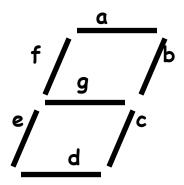

#### BCD-to-Seven-Segment Decoder: SEGMENT LABELS

Carpinelli Figure 1.22: BCD-to-SEVEN-SEGMENT DECODERS: TRUTH TABLES for all SEVEN BOOLEAN FUNCTIONS

## Carpinelli Figure 1.23 (a): KARNAUGH MAP SIMPLIFICATION of TWO BOOLEAN FUNCTIONS

## Carpinelli Figure 1.23 (b): LOGICAL CIRCUITS IMPLEMENTING TWO BOOLEAN FUNCTIONS

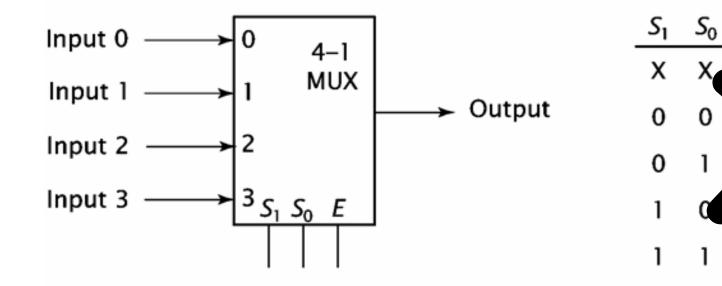

#### Carpinelli Figure 1.9 (a): MULTIPLEXOR

## Carpinelli Figure 1.9 (b), as it appears in the text:

#### Carpinelli Figure 1.9 (b), CORRECTED:

Original figure or table © 2001 by Addison Wesley Longman, Inc

Truth Table is now in <u>Counting Order</u>:

| E | $S_1$ | <b>S</b> 0 | Out     |  |

|---|-------|------------|---------|--|

| 0 | X     | X          | Z       |  |

| 1 | 0     | 0          | Input O |  |

| 1 | 0     | 1          | Input 1 |  |

| 1 | 1     | 0          | Input 2 |  |

| 1 | 1     | 1          | Input 3 |  |

Ε

0

X.

0

1

Output

put 0

put 1

Input 3

t 2

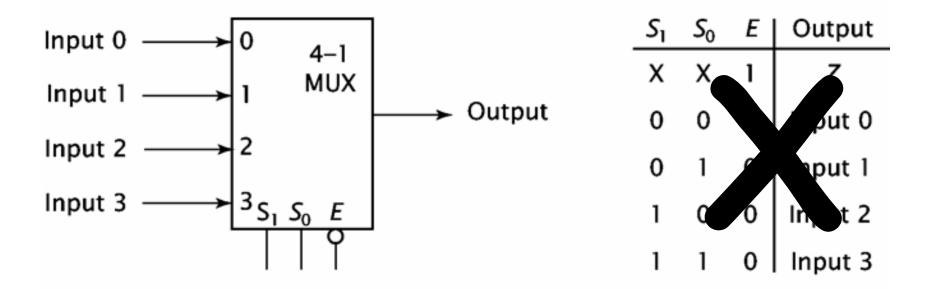

## Carpinelli Figure 1.9 (c), as it appears in the text:

## Carpinelli Figure 1.9 (c), CORRECTED:

Original figure or table  $\ensuremath{\mathbb{C}}$  2001 by Addison Wesley Longman, Inc

Truth Table is now in <u>Counting Order</u>:

| E | $S_1$ | <b>S</b> 0 | Out     |  |

|---|-------|------------|---------|--|

| 0 | 0     | 0          | Input O |  |

| 0 | 0     | 1          | Input 1 |  |

| 0 | 1     | 0          | Input 2 |  |

| 0 | 1     | 1          | Input 3 |  |

| 1 | X     | ×          | Z       |  |

## Carpinelli Figure 1.10: CONSTRUCTION of a 4-1 MULTIPLEXOR from THREE 2-1 MULTIPLEXORS

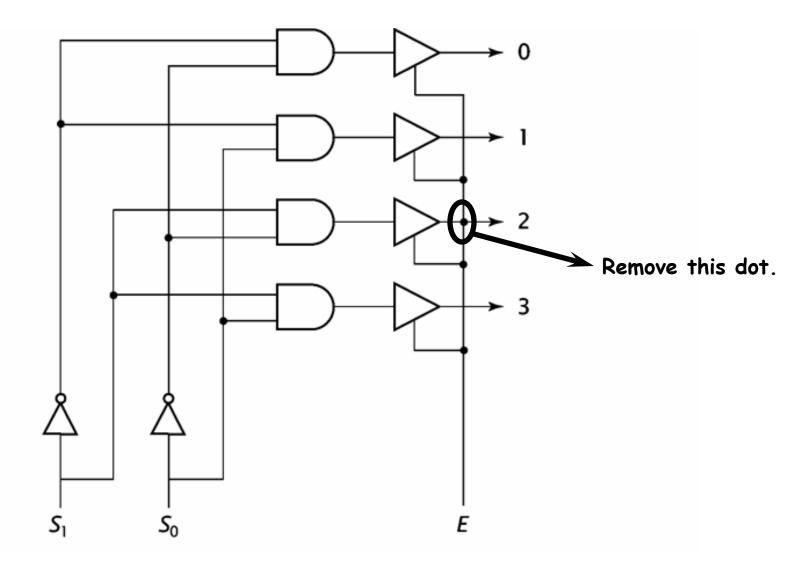

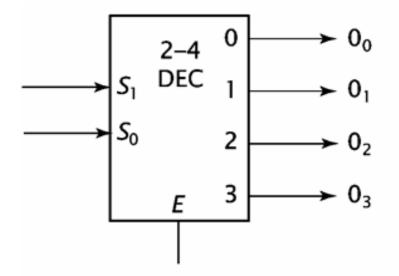

#### Carpinelli Figure 1.11 (a), as it appears in the text: DECODER

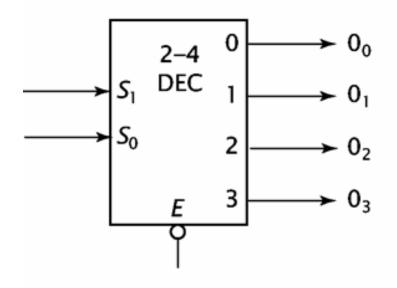

#### Carpinelli Figure 1.11 (a), showing CORRECTION:

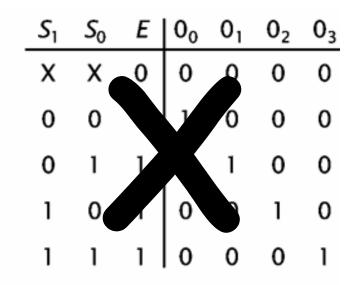

## Carpinelli Figure 1.11 (b), as it appears in the text:

#### Carpinelli Figure 1.11 (b), CORRRECTED:

Original figure or table  $\ensuremath{\mathbb{C}}$  2001 by Addison Wesley Longman, Inc

Truth Table with several corrections, and in Counting Order:

| Ε | <b>S</b> 1 | <b>S</b> <sub>0</sub> | Out <sub>0</sub> | <i>Out</i> <sub>1</sub> | <i>Out</i> <sub>2</sub> | Out <sub>3</sub> |

|---|------------|-----------------------|------------------|-------------------------|-------------------------|------------------|

| 0 | X          | X                     | Ζ                | Ζ                       | Ζ                       | Ζ                |

| 1 | 0          | 0                     | 1                | 0                       | 0                       | 0                |

| 1 | 0          | 1                     | 0                | 1                       | 0                       | 0                |

| 1 | 1          | 0                     | 0                | 0                       | 1                       | 0                |

| 1 | 1          | 1                     | 0                | 0                       | 1                       | 1                |

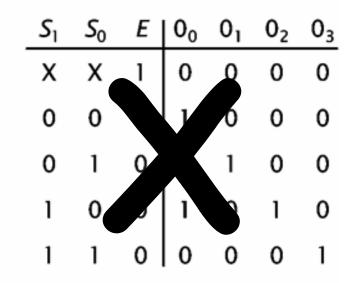

#### Carpinelli Figure 1.11 (c), as it appears in the text:

#### Carpinelli Figure 1.11 (c), CORRECTED:

Original figure or table © 2001 by Addison Wesley Longman, Inc

Truth Table with several corrections, and in Counting Order:

| Е | $\boldsymbol{\mathcal{S}}_{1}$ | <b>S</b> 0 | Out <sub>0</sub> | <i>Out</i> <sub>1</sub> | <i>Out</i> <sub>2</sub> | Out <sub>3</sub> |

|---|--------------------------------|------------|------------------|-------------------------|-------------------------|------------------|

| 0 | 0                              | 0          | 1                | 0                       | 0                       | 0                |

| 0 | 0                              | 1          | 0                | 1                       | 0                       | 0                |

| 0 | 1                              | 0          | 0                | 0                       | 1                       | 0                |

| 0 | 1                              | 1          | 0                | 0                       | 1                       | 1                |

| 1 | X                              | X          | Z                | Z                       | Z                       | Z                |

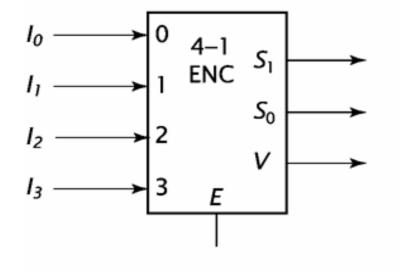

## Carpinelli Figure 1.12 (a): SIMPLE ENCODER

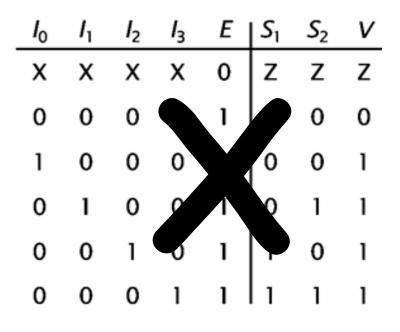

#### Carpinelli Figure 1.12 (b), as it appears in the text:

# Carpinelli Figure 1.12 (b), CORRECTED:

Original figure or table © 2001 by Addison Wesley Longman, Inc

Abbreviated Truth Table in Counting Order (not all input combinations are shown, since external constraints *allow* <u>at most</u> one input line to have a value of 1):

| E | I <sub>3</sub> | <b>I</b> <sub>2</sub> | <b>I</b> 1 | $I_{O}$ | $\boldsymbol{S}_1$ | <b>S</b> <sub>0</sub> | V |

|---|----------------|-----------------------|------------|---------|--------------------|-----------------------|---|

| 0 | X              | X                     | X          | X       | Ζ                  | Ζ                     | Ζ |

| 1 | 0              | 0                     | 0          | 0       | 0                  | 0                     | 0 |

| 1 | 0              | 0                     | 0          | 1       | 0                  | 0                     | 1 |

| 1 | 0              | 0                     | 1          | 0       | 0                  | 1                     | 1 |

| 1 | 0              | 1                     | 0          | 0       | 1                  | 0                     | 1 |

| 1 | 1              | 0                     | 0          | 0       | 1                  | 1                     | 1 |

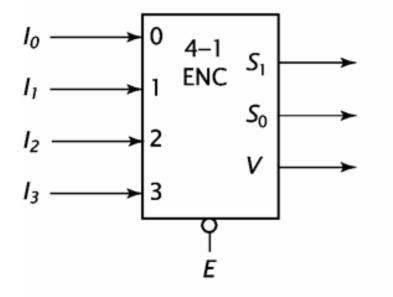

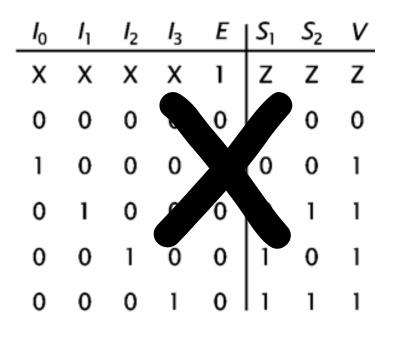

## Carpinelli Figure 1.12 (c), as it appears in the text:

# Carpinelli Figure 1.12 (c), CORRECTED:

Original figure or table © 2001 by Addison Wesley Longman, Inc

Abbreviated Truth Table in Counting Order (not all input combinations are shown, since external constraints *allow* <u>at most</u> one input line to have a value of 1):

| Ε | I <sub>3</sub> | <b>I</b> <sub>2</sub> | I <sub>1</sub> | $I_{O}$ | $\boldsymbol{\mathcal{S}}_{1}$ | <b>S</b> <sub>0</sub> | V |

|---|----------------|-----------------------|----------------|---------|--------------------------------|-----------------------|---|

| 0 | 0              | 0                     | 0              | 0       | 0                              | 0                     | 0 |

| 0 | 0              | 0                     | 0              | 1       | 0                              | 0                     | 1 |

| 0 | 0              | 0                     | 1              | 0       | 0                              | 1                     | 1 |

| 0 | 0              | 1                     | 0              | 0       | 1                              | 0                     | 1 |

| 0 | 1              | 0                     | 0              | 0       | 1                              | 1                     | 1 |

| 1 | X              | X                     | X              | X       | Ζ                              | Ζ                     | Ζ |

#### Carpinelli Figure 1.13 (a): PRIORITY ENCODER

Original figure or table  ${\rm \scriptsize C}$  2001 by Addison Wesley Longman, Inc

## Carpinelli Figure 1.13 (b) and (c) PRIORITY ENCODER (alternative version)

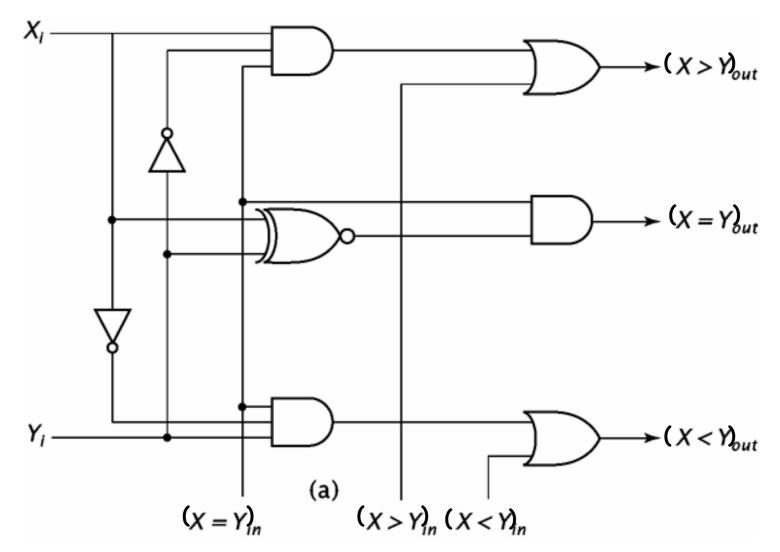

# Carpinelli Figure 1.14: ONE-BIT COMPARATOR

## Carpinelli Figure 1.15, as it appears in the text: SINGLE-BIT STAGE of a MULTI-BIT COMPARATOR

Original figure or table  ${\rm I\!C}$  2001 by Addison Wesley Longman, Inc

© 2003 Charles Abzug

#### Carpinelli Figure 1.15, CORRECTED: SINGLE-BIT STAGE of a MULTI-BIT COMPARATOR

Original figure or table  ${\rm I\!C}$  2001 by Addison Wesley Longman, Inc

© 2003 Charles Abzug

# Carpinelli Figure 1.16, as it appears in the text:

# Carpinelli Figure 1.16, CORRECTED:

$$0 \longrightarrow (X > Y)_{n} \quad (X > Y)_{ut} \rightarrow (X = Y)_{ut} \rightarrow ($$

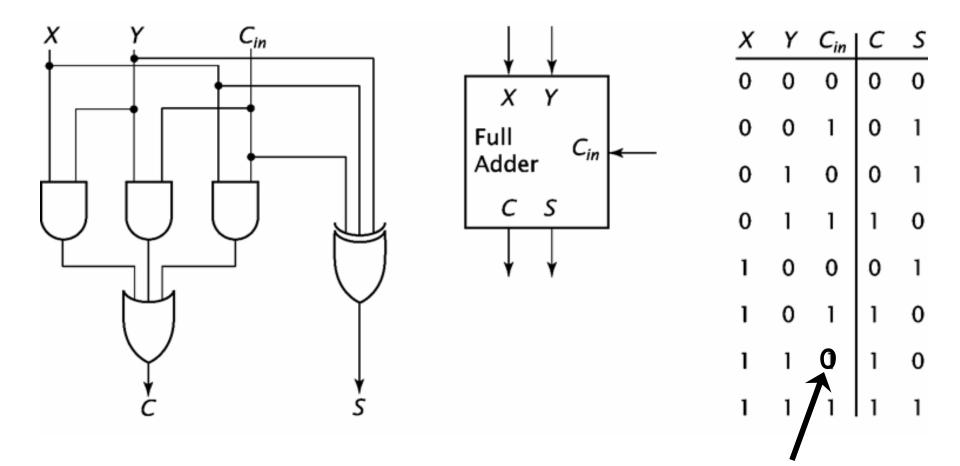

# Carpinelli Figure 1.17: HALF ADDER

# Carpinelli Figure 1.18, as it appears in the text: FULL ADDER

# Carpinelli Figure 1.18, CORRECTED: FULL ADDER

Original figure or table © 2001 by Addison Wesley Longman, Inc

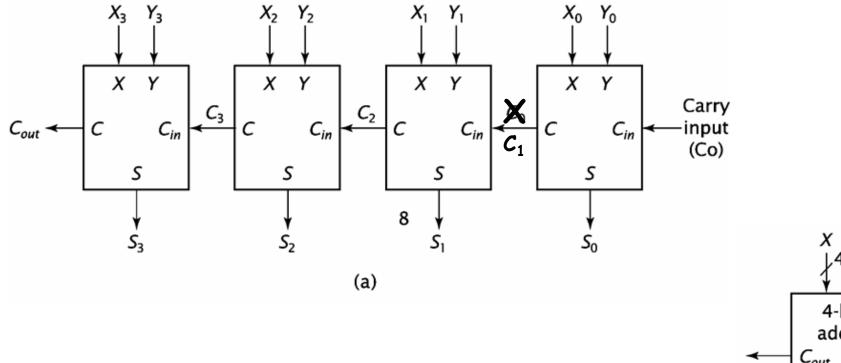

#### Carpinelli Figure 1.19, as it appears in the text: FOUR-BIT ADDER

## Carpinelli Figure 1.19, CORRECTED: FOUR-BIT ADDER

Original figure or table  $\odot$  2001 by Addison Wesley Longman, Inc

# Carpinelli Figure 1.20: SUBTRACTOR

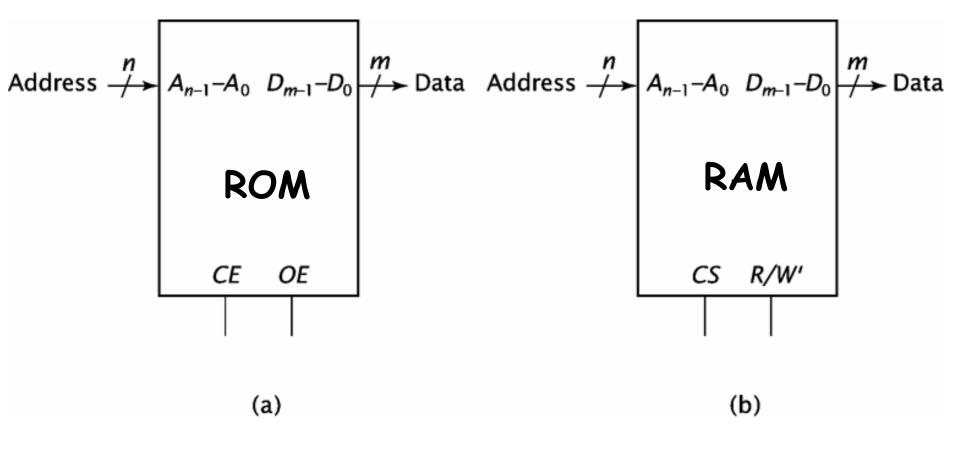

## Carpinelli Figure 1.21, as it appears in the text: MEMORY MODULES

## Carpinelli Figure 1.21, ENHANCED: MEMORY MODULES

Original figure or table  $\mbox{C}$  2001 by Addison Wesley Longman, Inc

# USE of MULTIPLE MEMORY MODULES

- 1. In general, a MEMORY consists of some number of addressable units, each of which is called a WORD.

- 2. The contents of a single word of memory are described as a string of bits. The words in a computer memory are all of identical width, *w*, and can be described as :

$D_{(w-1)} D_{(w-2)} D_{(w-3)} \dots D_{0}$

3. For a memory containing a total of T words, it is necessary to specify a numeric address in order to be able to uniquely identify each word. For this purpose, some number of address bits is necessary. The required number of address bits is given by:

$A \geq \lceil \log_2(T) \rceil$

4. We can construct the memory from a number of memory modules of equal size. If each module contains N words, then the individual module requires n address bits to specify which word within the module is to be accessed. Since N is always an exact power of 2,

$$n = \log_2(N)$$

# USE of MULTIPLE MEMORY MODULES (continued)

5. For a total of T words, the number of modules (memory chips) required is:

M = T/N  $\left[\log_2(M)\right] = \left[\log_2(T)\right] - \log_2 N$

6. The total address lines are thus divided into two groups: *m* chip-select lines, and *n* within-chip word-select lines:

$$A = m + n$$

- 7. The *n* within-chip address lines are connected in parallel to the addressselect input terminals of all of the memory modules.

- 8. The *m* chip-select lines go to an  $(m-x-2^m)$  decoder. Each output line from the decoder connects to the Chip-Enable input line of one memory chip.

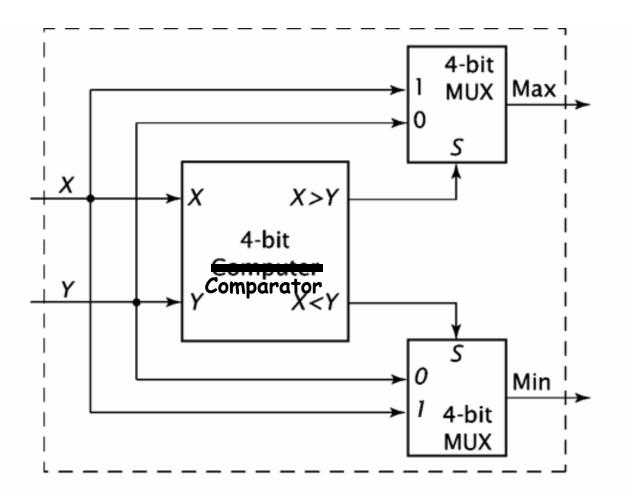

#### Carpinelli Figure 1.24 (a), as it appears in the text: TWO-NUMBER SORTER

#### Carpinelli Figure 1.24 (a), CORRECTED: TWO-NUMBER SORTER

Original figure or table © 2001 by Addison Wesley Longman, Inc

## Carpinelli Figure 1.24 (b): FOUR-NUMBER SORTER

## TWO PRINCIPAL TYPES of LOGIC CIRCUITS:

1. COMBINATIONAL

2. SEQUENTIAL

## TWO PRINCIPAL TYPES of LOGIC CIRCUITS:

#### 1. COMBINATIONAL

Current output (Os and 1s), after the passage of sufficient time to allow for circuit stabilization, is dependent solely upon current input (Os and 1s),

#### 2. SEQUENTIAL

Current output depends <u>not only</u> on current input, but also on the prior history of the circuit state.

# Carpinelli Figure 1.25

## Carpinelli Figure 1.26 (a): POSITIVE-EDGE-TRIGGERED <u>D</u> FLIP-FLOP

# Carpinelli Figure 1.26 (b): POSITIVE-GATED <u>D</u> LATCH

# Carpinelli Figure 1.27: POSITIVE-GATED D LATCH, with Asynchronous SET and CLEAR

# Carpinelli Figure 1.28: <u>SR</u> LATCH

## Carpinelli Figure 1.25: POSITIVE-EDGE-TRIGGERED <u>JK</u> FLIP-FLOP

## Carpinelli Figure 1.30: POSITIVE-EDGE-TRIGGERED <u>T</u> FLIP-FLOP

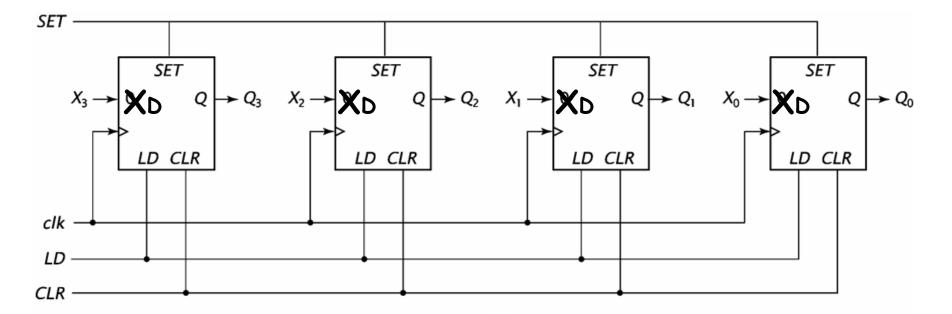

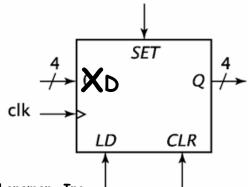

## Carpinelli Figure 1.31, as it appears in the text: FOUR-BIT REGISTER (*not* a 4-Bit Flip-Flop)

#### Carpinelli Figure 1.31, CORRECTED: FOUR-BIT REGISTER (*not* a 4-Bit Flip-Flop)

Original figure or table © 2001 by Addison Wesley Longman, Inc

#### Carpinelli Figure 1.32, as it appears in the text: Four-Bit Incrementing ("Up") Counter

Carpinelli Figure 1.32, *CORRECTED*: Four-Bit Incrementing ("Up") Counter

Original figure or table © 2001 by Addison Wesley Longman, Inc

© 2003 Charles Abzug

# Carpinelli Figure 1.33: FOUR-BIT INCREMENTING/DECREMENTING COUNTER ("Up/Down" Counter)

### Carpinelli Figure 1.34: FOUR-BIT LEFT-SHIFT REGISTER

Original figure or table © 2001 by Addison Wesley Longman, Inc

© 2003 Charles Abzug

### Carpinelli Table 1.8, as it appears in the text: SHIFT OPERATIONS

# Carpinelli Table 1.8, CORRECTED: SHIFT OPERATIONS

The corrected version corresponds to the definitions of the various types of shift operations typically implemented in the Arithmetic Logic Unit (ALU) portion of Central Processing Units (CPUs).

| Shift type                   | Mnemonic | X                                               |

|------------------------------|----------|-------------------------------------------------|

| Logical XXXXXXXXShift left   | shl      |                                                 |

| Logical kine and shift right | shr      |                                                 |

| Circular shift left          | cil      | $X_{2}X_{1}X_{0}X_{3}$                          |

| Circular shift right         | cir      | $X_0 X_3 X_2 X_1$                               |

| Arithmetic shift left        | ashl     | $X_{1} \times X_{1} \times X_{1} \times X_{0} $ |

| Arithmetic shift right       | ashr     | $X_{3}X_{3}X_{2}X_{1}$                          |

Original figure or table  $\mbox{\ C}$  2001 by Addison Wesley Longman, Inc

© 2003 Charles Abzug

### Carpinelli Figure 1.35: PROGRAMMABLE LOGIC ARRAY (PLA)

Original figure or table  $\ensuremath{\mathbb{C}}$  2001 by Addison Wesley Longman, Inc

### Carpinelli Figure 1.36: PROGRAMMABLE ARRAY of LOGIC (PAL)

### Carpinelli Problem 1.9:

F = WXY' + WXZ + W'XY + XYZ' = (WXY'Z + WXY'Z') + (WXYZ + WXY'Z) + (W'XYZ + W'XYZ') + (WXYZ' + W'XYZ')

### CARRY-LOOKAHEAD ADDER

$$\mathbf{g}_i = \mathbf{X}_i \wedge \mathbf{Y}_i$$

$p_i = X_i + Y_i (\underline{not} X_i \oplus Y_i)$

### FINITE-STATE MACHINES:

# SEQUENTIAL and COMBINATIONAL LOGIC

### Carpinelli Figure 2.1 (a): GENERIC STATE-MACHINE MODEL

## Carpinelli Figure 2.3: STATE DIAGRAMS for the JK FLIP-FLOP

#### Carpinelli Figure 2.4: JK FLIP-FLOP

State Table:

State Diagram:

# Carpinelli Figure 2.5 (b): STATE DIAGRAM for the MODULO-6 COUNTER: MOORE MACHINE

# Carpinelli Figure 2.6 (b): STATE DIAGRAM for the STRING-CHECKER: MOORE MACHINE

# Carpinelli Figure 2.A (b): STATE DIAGRAM for the STRING-CHECKER with REVISED STATE ASSIGNMENTS: MOORE MACHINE

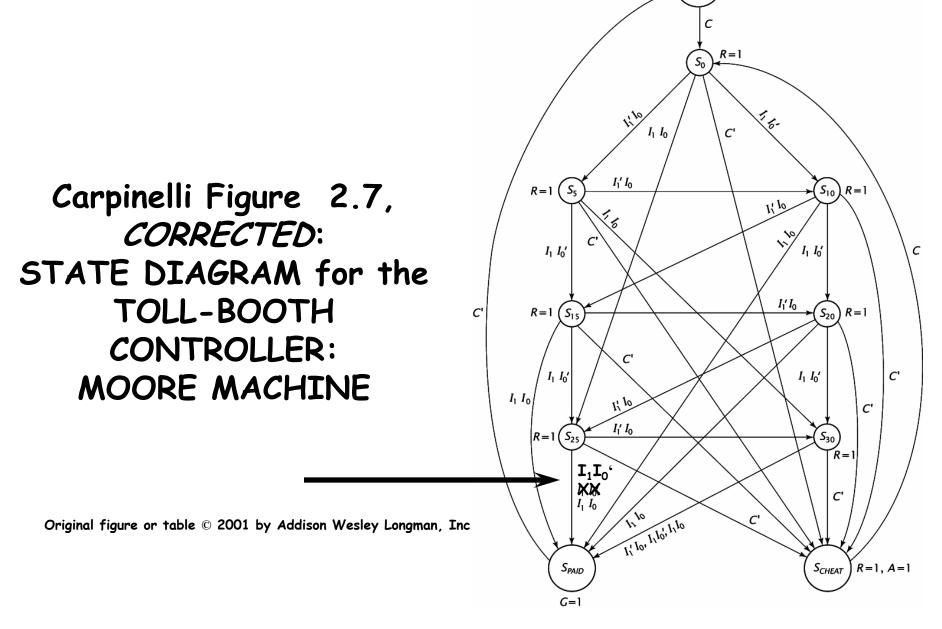

Carpinelli Figure 2.7, as it appears in the text: STATE DIAGRAM for the TOLL-BOOTH CONTROLLER: MOORE MACHINE

S<sub>NOCAR</sub>

R = 1

# Carpinelli Table 2.5: STATES for the TOLL-BOOTH CONTROLLER: MOORE MACHINE

# Carpinelli Table 2.6: STATE TABLE for the TOOL-BOOTH CONTROLLER: MOORE MACHINE

Carpinelli Figure 2.8 (b): STATE DIAGRAM for the MODULO-6 COUNTER: MOORE MACHINE (Assigned State Values Included

# Carpinelli Figure 2.10 (a): GENERIC MOORE MACHINE

# Carpinelli Figure 2.10 (b): MOORE MACHINE IMPLEMENTATION of the MODULO-6 COUNTER

# Carpinelli Figure 2.11: KARNAUGH MAPS for the NEXT STATE of the MODULO-6 COUNTER

# END